Selon les rapports, Samsung Electronics a produit avec succès une plaquette de travail DRAM basée sur l'architecture 4F² pour la première fois au monde, dépassant la limite de rétrécissement physique à laquelle la DRAM planaire traditionnelle est depuis longtemps confrontée. Il est rapporté qu'en février de cette année, Samsung a présenté publiquement pour la première fois ce prototype de DRAM de 16 Go intégrant l'architecture 4F² lors de la conférence ISSCC 2026.

Samsung a terminé la production de tranches en utilisant le processus 10a en mars et a confirmé le fonctionnement normal de la tranche grâce à des tests caractéristiques. Cette réalisation constitue la première pratique au monde intégrant la structure cellulaire 4F² et la technologie des transistors à canal vertical (VCT).

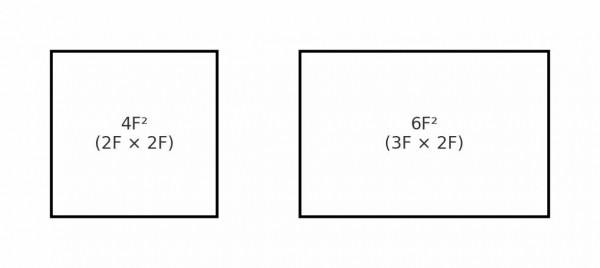

Techniquement, l'architecture 4F² réduit la surface unitaire de la DRAM traditionnelle de 6F² à une structure carrée 2F×2F, ce qui peut théoriquement augmenter la capacité par unité de surface de 30 % à 50 % tout en prenant en compte les avantages de vitesse et de consommation d'énergie.

Afin de réaliser cette structure, Samsung a introduit la technologie VCT pour ériger verticalement le canal du transistor et augmenter la longueur du canal dans la zone limitée de la puce, atténuant ainsi efficacement l'effet de canal court et les problèmes de fuite rencontrés par les transistors planaires traditionnels lors de la mise à l'échelle.

D'autre part, Samsung utilise la technologie de liaison hybride en cuivre entre tranches pour séparer le réseau de cellules de mémoire et les circuits périphériques sur différentes tranches, puis les empiler verticalement pour obtenir une interconnexion ultra haute densité.

Le matériau du canal est également modifié du silicium traditionnel à l'oxyde d'indium-gallium-zinc (IGZO) pour supprimer le courant de fuite dans les cellules qui rétrécissent.

À l’avenir, les puces DRAM de même taille pourront être emballées avec davantage d’unités. Les terminaux tels que les ordinateurs portables et les smartphones fins et légers devraient atteindre une plus grande capacité de mémoire et un débit de données plus rapide dans le cadre d'une petite taille et d'une faible consommation d'énergie.

Samsung a prévu une feuille de route claire pour cela : terminer le développement de la DRAM 10a en 2026, effectuer des tests de qualité en 2027 et passer à la production de masse en 2028.

SK Hynix prévoit d'introduire 4F²+VCT au nœud 10b, tandis que Micron maintient la voie de conception existante. Les fabricants chinois déploient directement la DRAM 3D en raison des restrictions EUV.