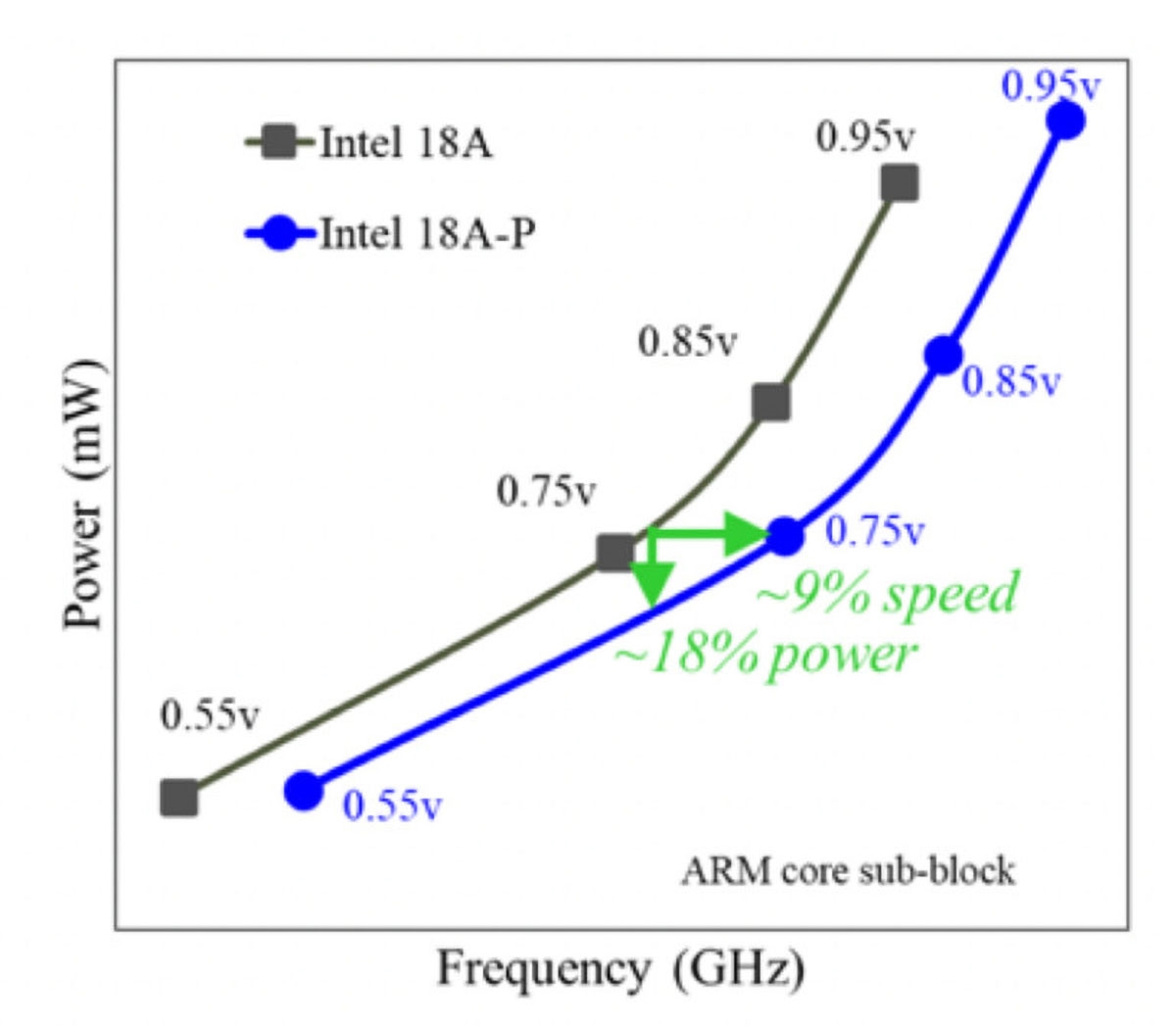

Intel a officiellement annoncé les données techniques clés du nœud de processus Intel 18A-P via le document T1.2 lors du séminaire VLSI 2026 tenu à Honolulu, Hawaï. Par rapport au nœud Intel 18A standard, le 18A-P permet un gain de performances de plus de 9 % pour la même consommation d'énergie et réduit la consommation d'énergie de plus de 18 % pour les mêmes performances.

Ces types d'améliorations de performances et de puissance, généralement constatées uniquement avec les transitions de nœuds entre générations, peuvent désormais être obtenues avec le 18A-P à la même densité.

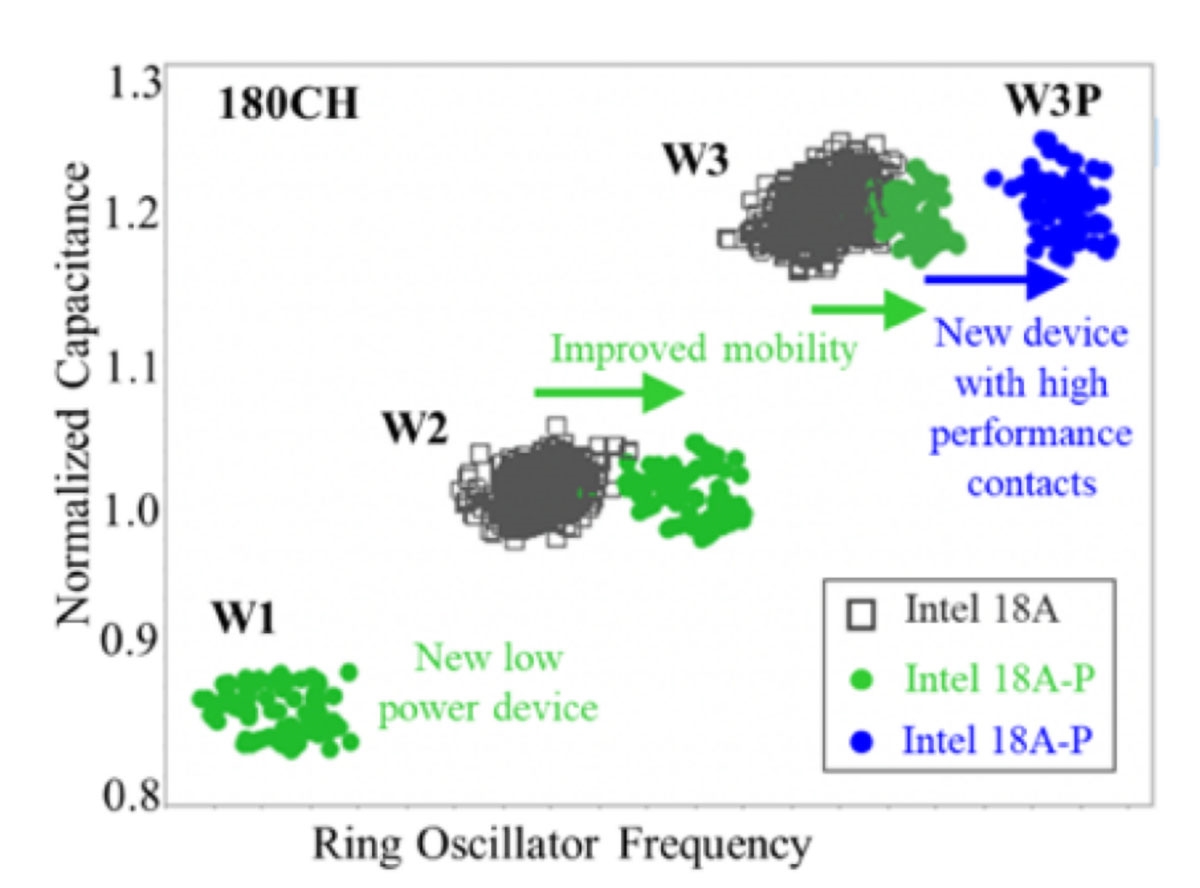

Le document Intel original répertorie quatre améliorations spécifiques : des paires logiques VT supplémentaires, un contrôle plus strict de l'angle de décalage d'horloge, de nouveaux périphériques basse consommation dans les bibliothèques haute densité (HD) et hautes performances (HP), et des versions aux performances améliorées des périphériques HP dans les deux bibliothèques.

Intel a réduit les angles d'inclinaison du 18A-P d'environ 30 % par rapport au 18A standard. La différence de performances entre les transistors sur la même tranche est considérablement réduite, la consommation d'énergie et les caractéristiques de performances sont plus prévisibles, et le rendement des paramètres et la cohérence de la puce sont simultanément améliorés.

En termes de dissipation thermique, la résistance thermique du 18A-P est environ 50 % inférieure à celle du 18A et l'efficacité de la conductivité thermique est grandement améliorée. Ceci est particulièrement critique pour un fonctionnement durable à haute fréquence dans les scénarios de calcul hautes performances, et répond également directement aux défis de dissipation thermique posés par la technologie d'alimentation arrière (PowerVia).

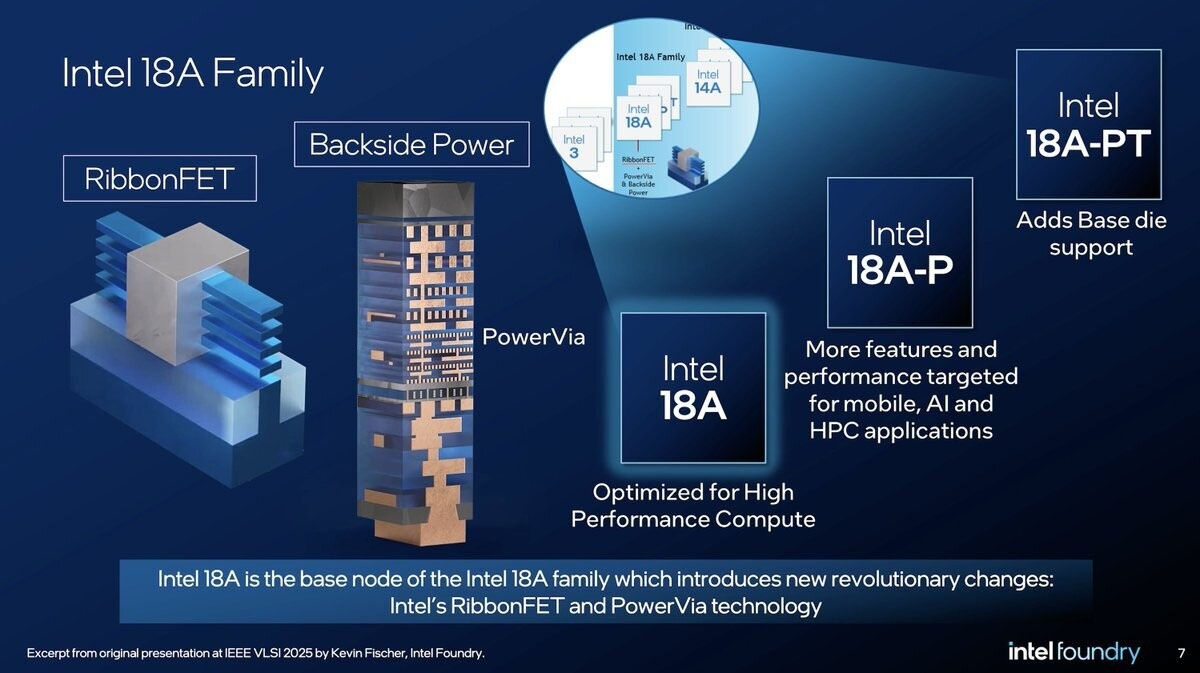

Intel a expédié la version 1.0 de son kit de conception de processus PDK pour 18A-P à des clients potentiels afin de leur permettre de commencer à tester la vérification des puces. Ce processus est toujours basé sur l'architecture de transistor à grille polyvalente RibbonFET et la technologie d'alimentation arrière PowerVia, et constitue une version aux performances améliorées de la plate-forme 18A.

Selon TrendForce, Apple évalue l'utilisation du procédé 18A-P pour produire des puces de la série M, tandis que Google envisage d'utiliser la technologie de packaging avancée EMIB d'Intel pour promouvoir le projet TPU v8e. Les produits associés pourraient être lancés dès 2027.